一、雷达电子对抗原理

雷达对抗是指从敌方雷达及其武器系统获取信息(侦察),破坏和扰乱敌方雷达及其武器系统得正常工作的战术、技术措施的总称。雷达对抗设备中的接收机用于截获雷达信号,由于接收机输入信号未知,所以相对于通信、雷达接收机等而言,具有频带宽、实时性强的特点。传统雷达对接收机输入信号通过视频检波器变换成视频信号,视频信号再进一步处理产生脉冲描述字(PDW),随着模-数转换器(ADC)的采样率及信号处理器的处理速率的提高,下变频后的信号,可以被高速ADC直接量化,再通过数字信号处理产生需要的PDW。相对于采用视频检波器的接收机来说,数字化接收机更稳定可靠,没有模拟电路中的温漂及直流电平变化等,且采用高分辨力谱估计技术,可以得到更加精确的频率分辨率。超高速数据采集技术研究是数字接收机的一个重要方面,对提高数字接收机的瞬时带宽,实时截获雷达信号具有重大意义,本文介绍了一个具有高采样率、高速数据传输的数据采集板的设计,成功应用于某雷达对抗设备上。

二、雷达电子对抗对超高速数据采集的需求分析

2.1 基本原理

数据采集的主要任务是将雷达信号进行模数变换和存储,并将数据以要求的数据率和格式传输给后续系统。

2.2 数据采集的需求

1、超宽带宽:大于1.2GHz,

2、采样率:大于2.4GHz

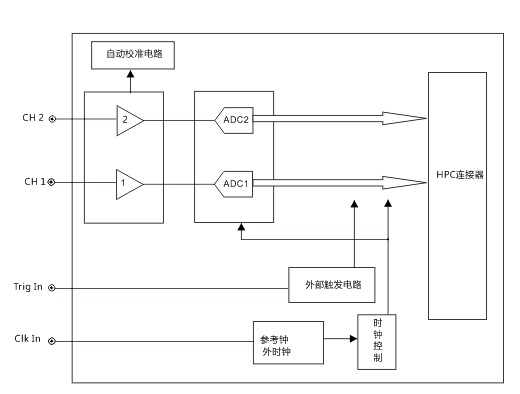

3、采用超宽带模拟正交解调、I、Q两路解调信号分别采样,采样率选择1.6GSPS.

4、FPGA要进行高速的数据传输。

5、采样时钟采用具有分频、移相等功能的时钟管理芯片。

6、具有电路模块化、通用化的要求。

高速数据采集系统框图

2.3 AD数据采集卡的选择

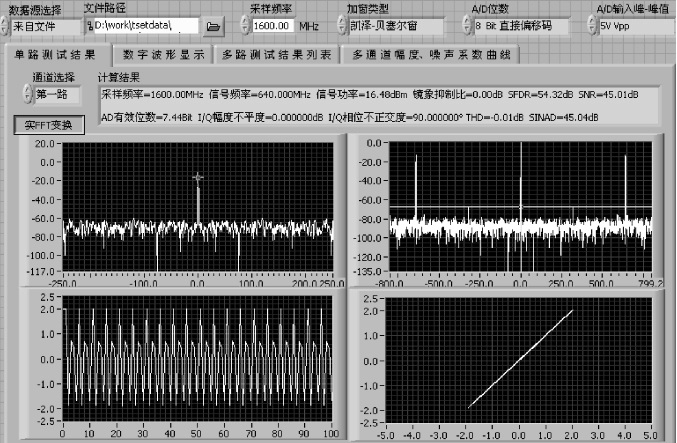

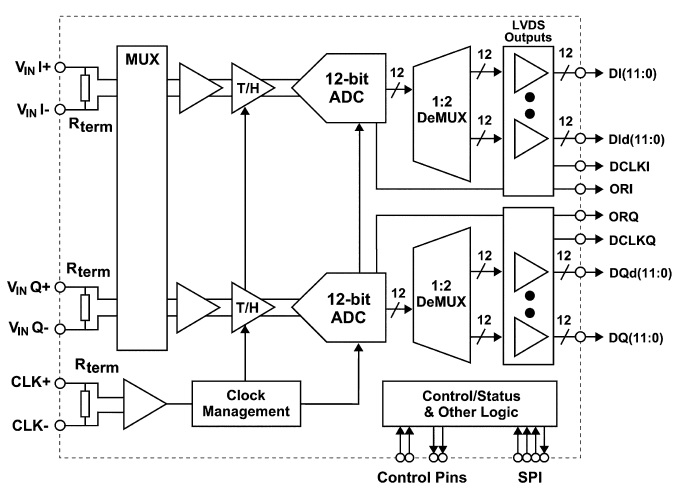

根据客户的要求,我们推荐选择FanRet推出的Brave系列中的FS12300,该卡的ADC选择TI公司的12bit 3.6GSPS 芯片ADC12D1800RF, 时钟芯片选择ADI公司的AD9516-4,其主要指标如下:

l 分辨率:12bit

l 采样率:单通道3200MSPS

双通道1600MSPS

l ENOB: 8.7bit

l SNR: 54dB

l SFDR: 60dBc

l BW: 2.7GHz(-3dB)

l 数据接口:DDR-LVDS;

ADC(ADC12D1800RF)前端设计有两个耦合方式,这里采用变压器交流耦合方式。采用MABA-007159-000000巴伦变压器完成,巴伦变压器的主要作用是完成由单端传输变换为差分传输,并且MABA-007159-000000的带宽是4.5MHz~3GHz,能够很好的满足ADC(ADC12D1800RF)输入带宽的要求。ADC12D1800RF使用差分时钟源,时钟源的相位噪声尽可能的低,如果时钟频率确定,可以增加时钟滤波电路来提高时钟的性能。

三、客户使用后的二次开发

FanRet提供SDK二次开发软件包,并且提供FPGA的资源开放,客户可以根据自己的需求编程算法进行数据处理。